這一單元所要介紹的是PLL中的環間濾波器(loop filter)和壓控振盪器(voltage control oscillator),雖然第一單元中說過要避免枯燥,但是一提到濾波器難免會要動用一些煩人的數學式子,既然無法避免,那只好忍耐地期待「柳暗花明又一村」了。以下所述的環間濾波器有簡單的被動RC型及主動濾波器,但都以一階及二階為主。另外提出一個比較複雜的諾頓型濾波器,並附一個BASIC程式,以求其RC元件值,至於有關環間濾波器為了改善諧波排斥,(頻)寬(Bandwidth)等,而重新設計,或二個並聯使用,或加用一個低通濾波器,或加用一些元件等均在討論範圍之內。至於VCO IC,一般常看到的都是VCM,也就是方波輸出,而在類比應用中,VCO一般指的是正弦波,最常用的是在線路中套用一個變容二極體,利用電壓來改變電容,進而控制振盪頻率。

環間濾波器

環間濾波器在PLL系統中的主要功能有二:第一是去除從相位比較器輸出的雜訊或高頻成份,它類似電源線路的整流濾波,以提供比較純的直流電壓輸出來控制壓控振盪器。第二是它幾乎主宰著整個PLL的動態特性,像是捕捉範圍(capture range)、鎖住範圍(locked-in range)、動作寬度(Band-width)、暫態響應(transient response)等。

基本上環間濾波器是低通組合,因此理論上,只要懂得濾波器設計再加上對相鎖環的一些要求能夠滿足,就能設計很好的環間濾波器。因為簡單的RC線路常在實際使用上出現,因此先來看看RC一階低通組合。

圖一是一階RC低通濾波器,其截止頻率(cutoff frequency)Wcut=1/RC徑/秒,利用此截止頻率來表示其環自然頻率(loop natural frequency)Wn,Wn=(KϕKoWcut)½,其中Kϕ、Ko分別是相位比較轉換增益及壓控振盪轉換增益,前者單位是伏/徑,後者單位是徑/秒/伏。若用K=Kϕ.Ko來代替,則Wn=(K/RC)½。另外一種稱做阻尼因子者(damping factor),DF=½(Wc/Kϕ.Ko)½。現在我們來看看第一單元圖二中,RC環間濾波器R=4.7KΩ,C=10uF,因此其截止頻率Wcut=1/RC=21.28徑/秒=3.39Hz(因為W=2πf),又因其Kϕ=5V/2π(使用的是flip-flop型),Ko=58/5V,故K=(5/2π).(58/5)=9.23,所以√Wn=KWc=(9.23x21.28)½=14徑/秒=2.23Hz,而阻尼因子DF=½(Wc/K)½=½√21.28/9.23≒0.76。

上面導推與設計的程序相反,但是這樣我們可以大致了解這些參數值的範圍,至於如何設計,又Wn及阻尼因子如何選擇呢?

阻尼因子的選擇

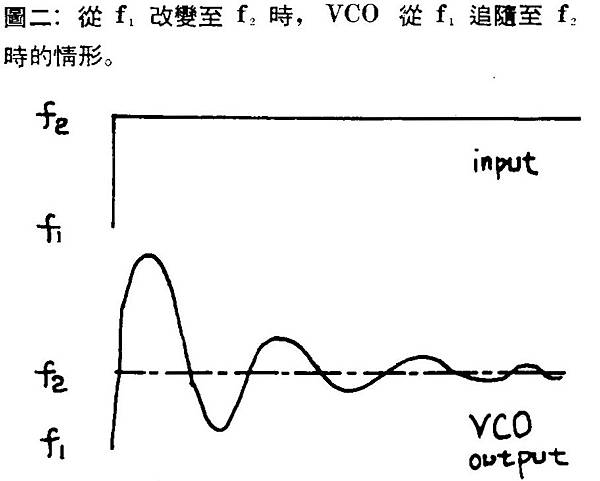

在PLL系統中,當相位比較器的參考輸入或從VCO來的訊號輸入從f1位移至f2頻率時,必然的,VCO部分會改變以追隨從f1改變至f2,在這種f1改變至f2的過程中會有如圖二的反應,而阻尼因子也就是控制著從f1改變至f2所需的時間,當阻尼因子越大,完成的時間越短,但是阻尼因子在大於1時便開始有產生振盪的傾向,而阻尼因子下降時,則改變的時間會隨之加長,因此最適宜的阻尼因子是介於0.5~0.8之間。

上述設計組尼因子等於0.76,也就是守這個原則。下面我們舉個實際設計的例子:例如利用RC低通環兼濾波器,欲使PLL系統的阻尼因子為0.5,並且必須在改變頻率後的10毫秒內,使VCO輸出是在穩定狀態(steady-state)的10%之內,如何求RC值,以設計此環間濾波器?首先必須由暫態響應圖表求出設定時間(setting time)Wnts,由圖三中,當阻尼因子=0.5時,在10%之內的Wnts=4.5,又因為我們要求ts=10毫秒,故Wn=4.5/10-2=450徑/秒,假設K=Kϕ.Ko=9.0,那麼Wn=(K.Wcut)½則Wcut=22500=1/RC,我們選擇C=0.01uF則R≒4.4KΩ,那麼只要利用4.4KΩ的電阻和0.01uF的電容組合成如圖一的線路,就可以滿足上述的PLL系統要求。

若看到或想用上述另外兩種環間濾波器時,只是其Wn及阻尼因子DF的式子不同而已,其設計步驟filter來看看,其使用的是lag-lead low-pass filter,從這個製作中我們來看一看其Wcut、Wn及DF。

參看圖四中,其Wcut=[(R18+R19)]-1=[102.2x103.1x10-6]-1=9.8,u.4K=Kϕ.Ko,其中Kϕ=10V/π,Ko=1MHz/10V,故K=10V/π.(1x106/2π)/10V≒50660.6,故Wn=(K.Wcut)½=(50660x9.8)½≒705,阻尼因子DF=Wn/2[R19C6+1/K]=0.78。在實際設計時,可以參看IC的Data sheet,像CD4046的loop filter在Data sheet上均有詳細說明。

有關環間濾波器的問題

在某些PLL應用中,往往需要有極大的輸出頻率範圍,像是頻率合成的應用,例如頻率合成訊號產生器(參看音響技術第89期95頁),因此對於環間濾波器的要求就更加嚴格,所以一個PLL系統可能要兩個或兩個以上的環間濾波器以應實際需求,如圖五所示(原圖參看P.139, Electronics March 10, 1982,原設計者是Yekutiel Joefsberg)。一個窄路濾波,一個寬路濾波,兩個相並聯。

通常變換環間濾波器時,在開關變換的剎那容易產生失鎖,但如圖五的設計加上一個緩衝器,可以避免這種情形發生,當PLL系統打開時,S1及S2關閉,這時寬路濾波(Wide bandwidth loop filter)產生作用所以比較容易進入鎖住狀態,在PLL系統鎖住之後,S1及S2打開而回到窄路濾坡時,因C1已充電至可以鎖住的正確電壓,因而不會有暫態反應出現,自然S1及S2的開關變換就不會影響已經鎖住的狀態,至於S1及S2打開之後C1要達到與C2同電壓所需的時間長短與S2閉態電阻、緩衝器的輸出阻抗大小、以及C1值的大小有關。

至於S1及S2如果能利用像是4016或4046之類的電子開關,而由「失鎖指示」的電壓來控制,如此一來,一旦PLL系統因故失瑣時能自動關閉S1及S2以打開寬路濾波而很快地就能再回到鎖住狀態。

另外在PLL的倍頻或頻率合成的應用中,如音技89期99頁的頻率合成式訊號產生器的應用,尤其是利用主動環間濾波器時,很容易感染偶諧波(even-ordwr harmonics),如何去除這種惱人的諧波呢?

圖六B中其轉換函數為F(S)=(Sr2+1)/Sr1,其中r1=R1C, r2=R2C,但是圖六C中,在R2兩端並接一個電容C'時,其轉換函數 F'(S)=(S)=Sr+Sr3+1)/(S2r1r2+Sr1),r3=R2C' 參看圖六C及圖六D,當W3=W2f 時會開始漸漸衰減而降低對偶數諧波的感應(相同的情形,請參看第一單元中圖二在相位比較器前加用低通濾波器),雖然加上了C'之後可能造成某些不穩定的情況發生,並且影響了阻尼因子及系統(頻)寬,所以,雖然改善了諧波出現,但是,一旦降低諧波輸出,相對地必須犧牲一部分PLL的操作頻率範圍。微波的抑制情形可以用一個式子來表示,稱做S/C比(sideband-to-carrier ratio),它類似S/N比,其等式為S/C=20log(4BN/2fr),其中B是頻寬(Bandwidth),N是指頻率合成除環中的除數,fr是參考頻率,這是指假定未使用低通濾波器,若是在環濾波器之前加個低通濾波器如圖七所示(原稿分別參看Electronics, April 12, 1979, P150及March 10, 1982, p. 138)。

下面實際應用例子,例如要求S/C比為-50dB,而VCO的工作頻率是3MHz,參考頻率是100KHz,所以N=3000000/1000000=30,從圖七中查知N=30,S/C比為-50dB的交點是0.0053%.fr 而此時 fr=100x103,故B=5.3Hz,如果B要達到500Hz,那麼必須在環間濾波器之前加個低通濾波器才能使S/C比保持在-50dB,因為B=500(Hz),故從圖七中新的B=0.5%.fr與N=30的交點是-10dB,故環間濾波器之前的低通濾波器必須負責-40dB,那也就是我們設計時所必須知道的參數;關於環間濾波器就講到這裡。

壓控振盪器(VOC)

如果細分,壓控振盪器可以分成好幾種,大家常見的555 IC也可以組成VCO。而實際上它們應該被稱作VCM比較妥切,就像74124也是一樣,由於VCO樣式多,而我們只要課題是在PLL,所以這裡只要提出典型的幾個例子來加以說明,在實際應用時,只要參考VCO方面的資料即可。壓控振盪器又名電壓──頻率轉換器(voltage-frequency conveter),也就是說輸出頻率大小是受外界電壓控制的,如同相位比較器一樣,它有個公式:Wo=Ko.V,其中Wo是輸出頻率(徑/秒),而V是控制電壓,Ko則是壓控振盪轉換增益。圖八是二個典型的VCO例子。

圖九是諾頓型主動濾波器(原圖參看Electronic Design May 10. 1980,原作者是Jack poter)這個環間濾波器使用諾頓(Norton)放大器而不使用OP-Amp,它可以去除外界雜訊使得PLL系統能穩定地工作,而且整個線路中的RC值可以由表一所列的BASIC程式算出來。

這個程式run之後,只要輸入阻尼因子(damping factor),無阻尼自然頻率(Undamped natural frequency)及濾波器截止頻率(filter cutoff frequency)和相位比較參考頻率(Phase-detector refequency)之後,符合這些條件的線路R、C值馬上可以算出來。

以上二單元可能會枯燥些,下一單元開始討論PLL的應用之後,可能會生動一些,由於PLL的應用的確牽涉廣泛,但我們仍然儘可能的詳盡介紹,上述這二單元果真看不下去的話,可以等看過PLL應用之後再回頭來看。

轉載音響技術第95期NOV. 1983 PLL相鎖環初步運用──第二單元/林茂榮

留言列表

留言列表